课程信息

coursera VLSI CAD Part I: Logic and VLSI CAD Part II: Layout

Rob A. Rutenbar, The University of Illinois at Urbana-Champaign

课程目的

实现一个CAD工具,这个工具可以用来辅助设计semi-custom ASICs。

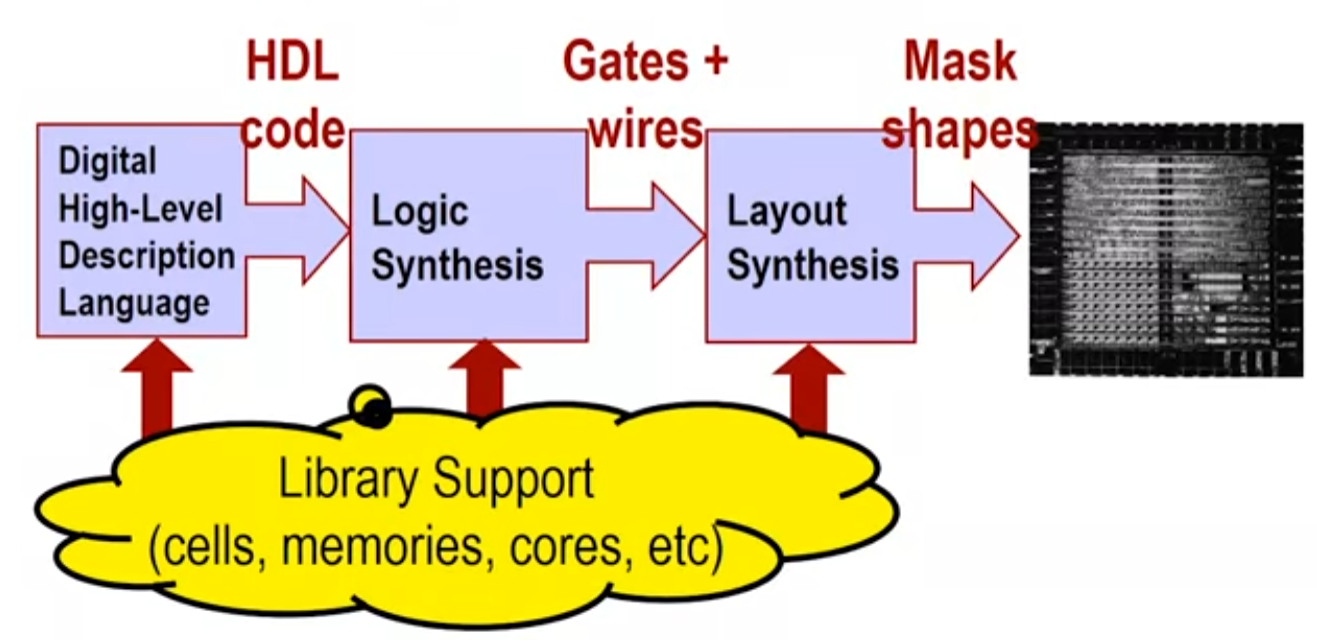

CAD负责从Logic Synthesis到流片之前的所有步骤。

名词解释

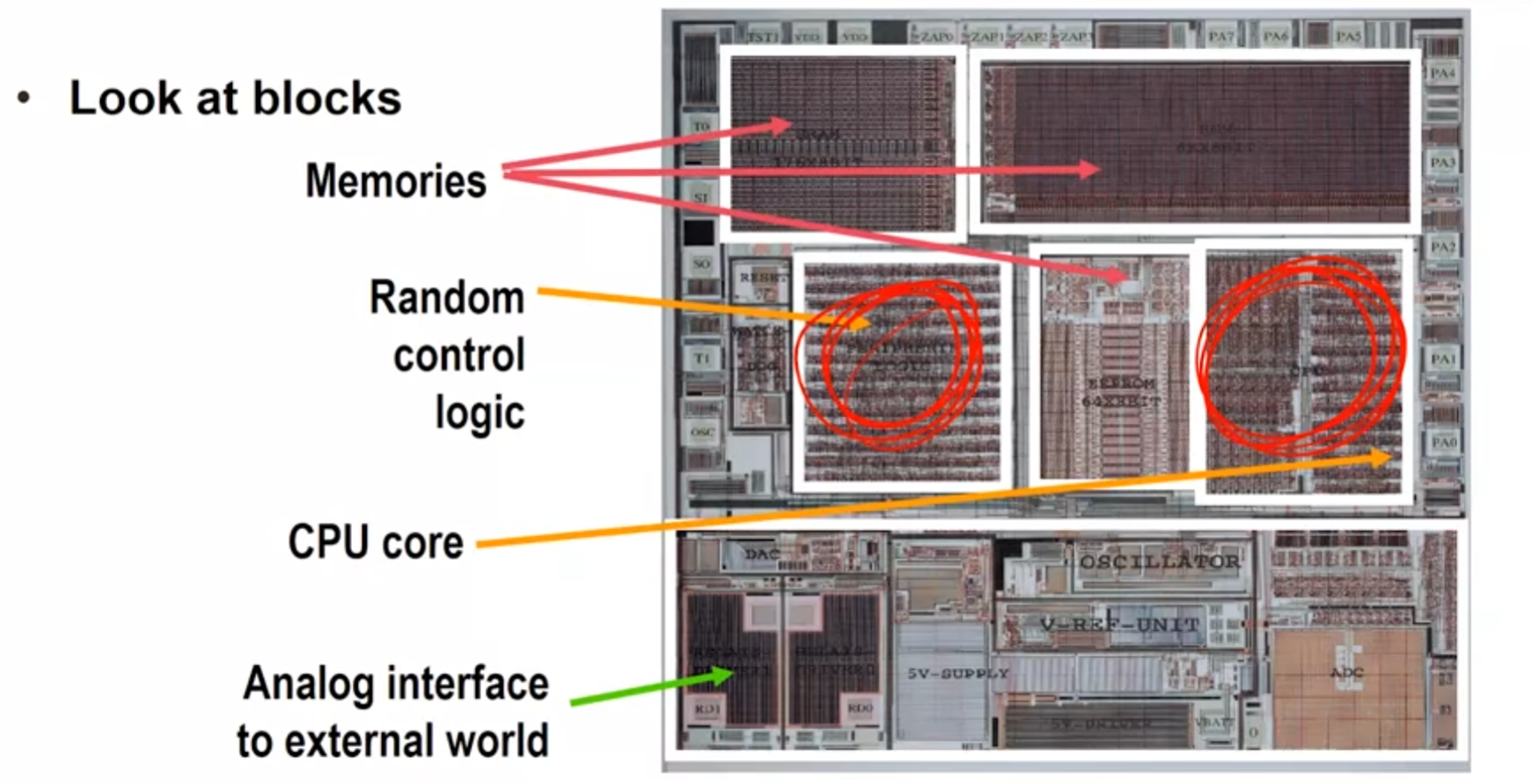

- ASIC, Application-Specific Integrated Circuit 为专门目的而设计的集成电路

- Semi-custom 复用已经设计好的部分电路

- CAD, Computer Aided Design, 计算机复制设计,此处指经过一系列设计步骤和软件工具的流程

- EDA, Electronic Design Automation 电子设计自动化

- SOC, System-On-a-Chip ASIC 片上系统,是一个有专用目标的集成电路,其中包含完整系统并有嵌入软件的全部内容

- CAD Flow, 把大的设计分解为若干步骤,全部的步骤称为一个Flow。从上往下越来越具体,从下往上越来越抽象。Synthesis/综合 是指从上到下走,Verification/验证 是指从下往上走。

本课程的两部分流程:

从布尔/逻辑设计的描述开始,到最后输出门电路和电线的坐标。

第一阶段的课程主题

- Computational Boolean Algebra 计算布尔代数

- Boolean Verification 布尔验证

- 2-Level Logic Synthesis 2级逻辑综合

- Multi-Level Logic Synthesis 多级逻辑综合

Computational Boolean Algebra Basics 计算布尔代数基础

Karnaugh maps 卡诺图

布尔函数的最小化

卡诺图方法只能化简不超过6个变量的布尔函数